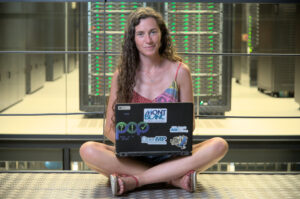

Introducing Marta Garcia-Gasulla

I am Marta Garcia-Gasulla, a team leader at the BSC computer science department.

I am a computer engineer from the Universitat Politecnica de Cataluna (UPC). I did a master’s in computer architecture and then a Ph.D. in computer architecture at UPC. For my PhD, I developed a runtime library that would improve the load balance of HPC applications: the DLB library. Load balancing is closely related to parallelization. When a piece of software is load balanced, it delegates work in parallel to the greatest number of processors so that work moves as quickly as possible without leaving calculations waiting for hardware to become available while other capable hardware is sitting idle. Dynamic load balancing (DLB) is when a piece of software can reallocate work as hardware becomes available in real-time while a task like a simulation is running.

Towards the end of my PhD, I started working with HPC software that was already being used by scientists and researchers. I realized that there is a gap between the field scientists who use HPC systems to solve a problem (like designing a more fuel-efficient airplane, and computer scientists who are developing the software and hardware for such systems. This was the starting point of the group that I lead: Best Practices for Performance and Portability (BPPP). In the BePPP team, we bridge this gap through the detailed performance analysis of HPC applications to help ensure that the software and hardware meets the needs of its future users.

At CEEC, I would like to help the lighthouse cases efficiently use computational resources, such as future Exascale HPC systems, by using existing features provided by the DLB library and developing new ones when needed.

I will also help the different codes involved in the project to run in the prototypes of the European emerging architectures (EPI and EUPilot projects). With this early analysis, we prepare the software for these architectures and can influence the details of its design.

My ultimate goal in the project is to understand the main performance issues that HPC applications are facing and help them find solutions to these challenges.

The part that I enjoy the most about my work is having contact with the scientists running their simulations, understanding the particularities of their simulations, and further understanding how these particularities affect the performance.

Comments

3 responses to “Introducing Marta Garcia-Gasulla”

[…] Now, you might ask, what happens when your parallelization meets adaptive mesh refinement and your “people” or processors find themselves with suddenly far more “blocks” to calculate in their assigned geometric space than in previous time steps? If the whole team had to wait on them, many other processors would be idle while they crunched through their extra work. This is precisely what dynamic load balancing (DLB) fixes. It’s the necessary flip side to adaptive mesh refinement. If processors suddenly find themselves falling behind the group, DLB steps in like a middle manager to reallocate work so that the team can stay on schedule and make the most efficient possible use of available hardware. If this sounds a little familiar, it’s because DLB is part of what Marta talked about in her PeopleOfCEEC profile. […]

[…] For Alya, the focus was on porting the structural mechanics solver’s assembly to GPU. Additionally, we were able to discuss the evaluation of a benchmark test related to lighthouse case 1 (High Fidelity Aeroelastic Simulation of the SFB 401 Wing in Flight Conditions) with Marta Garcia. […]

[…] Marta Garcia-Gasulla […]